## AI-Assisted Chip Design Tutorial

HotChips

**Stelios Diamantidis**

Synopsys Distinguished Architect

25 August 2025

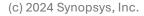

(c) 2024 Synopsys, Inc.

#### Al-driven Optimization for Chip Design

- 1. Motivation Why AI for Optimization

- 2. The Reinforcement-Learning Optimization Paradigm

- Search spaces, acquisition functions, metrics/KPIs, pareto fronts, learning

- 3. Applications of RL-driven Optimization

- Physical design, micro-architecture, search-based verification, test, analog, 3D exploration

- 4. Augmenting RL with GenAI A World of Opportunity

- Optionality vs. optimality, evolution of human-compute i/f, data abstractions

#### Disclaimer

- This is a technology tutorial

- Several examples have been drawn from Synopsys research in AI

- The capabilities presented may not be indicative of Synopsys products

- For product-related information, please contact Synopsys sales

# Motivation – Why Al for Optimization

Al-Assisted Hardware Design Tutorial – HotChips 2024

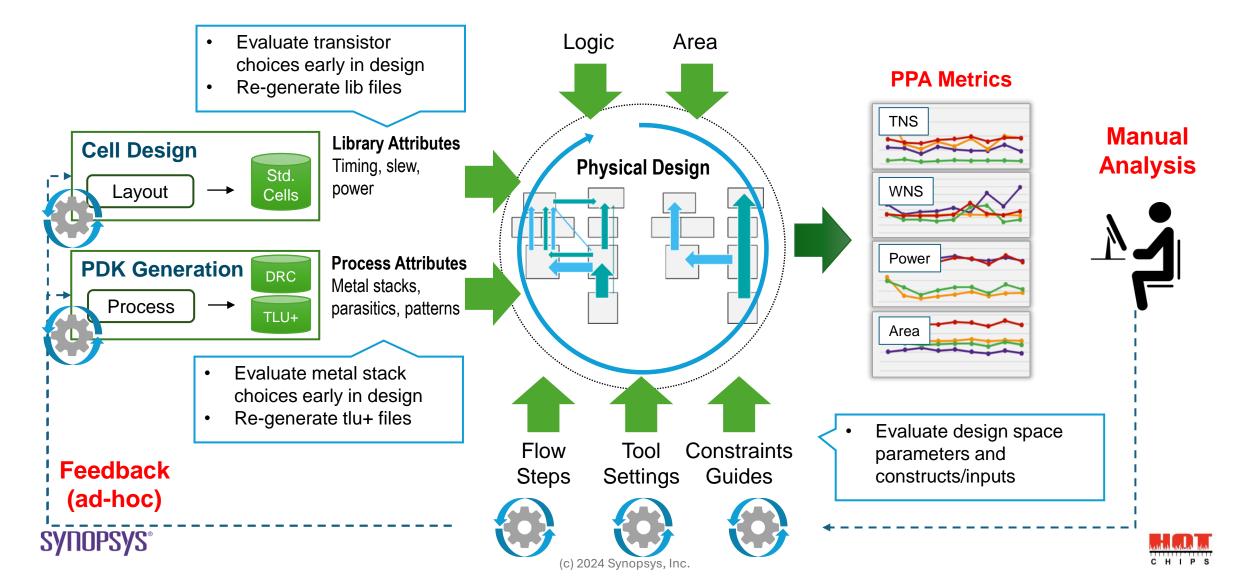

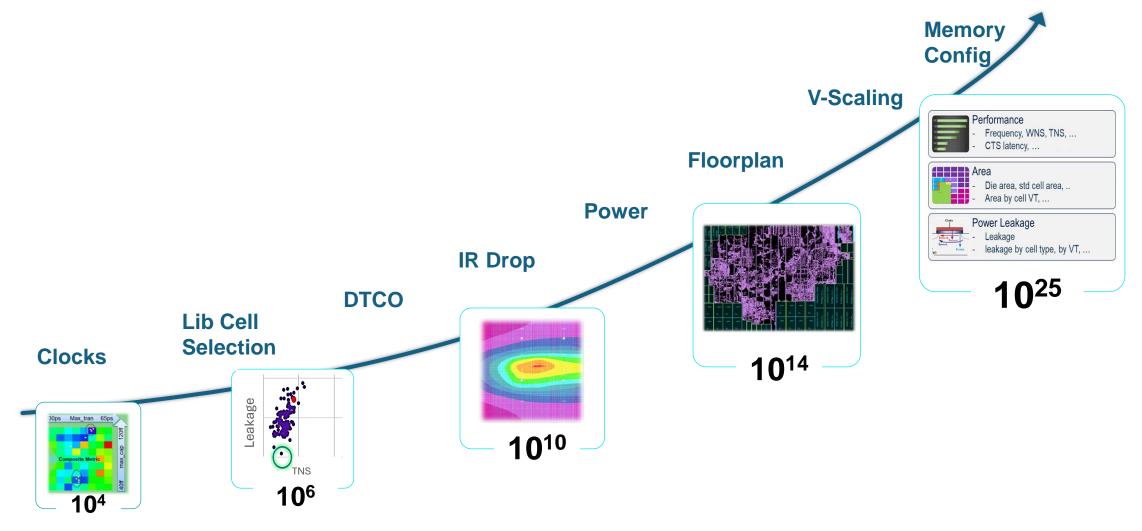

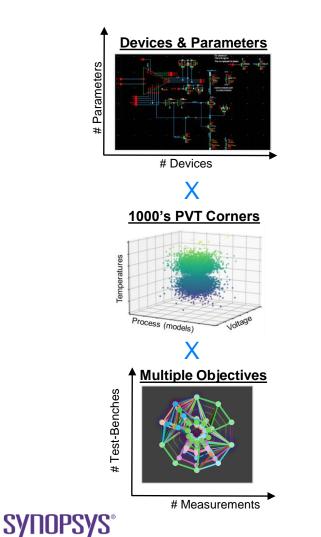

#### Chip Design: A Near-Infinite Problem Space

#### **Design Complexity Grows Exponentially**

**SYNOPSYS**<sup>®</sup>

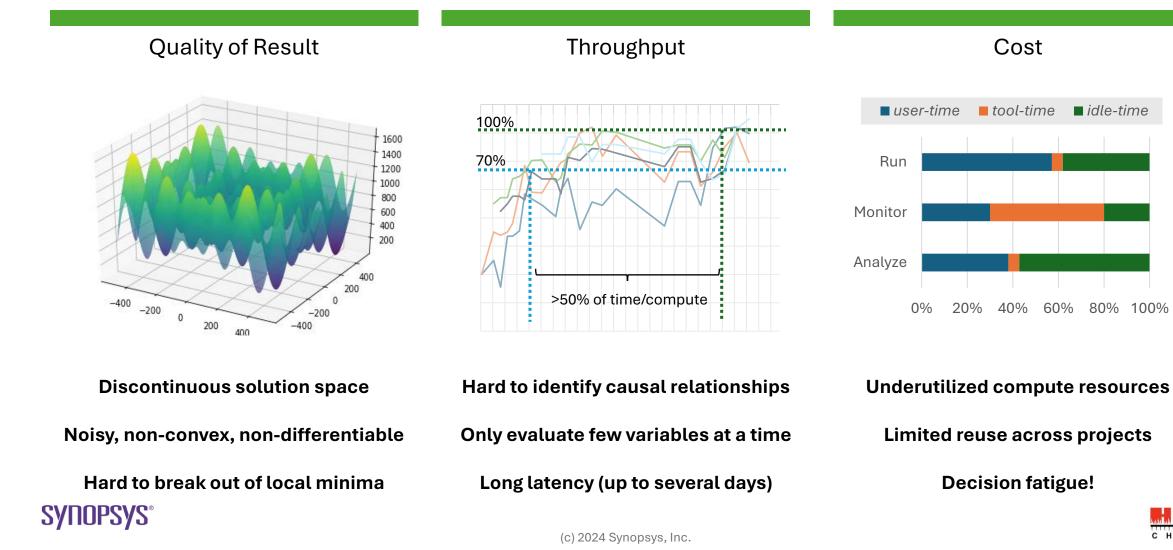

## Implication of Design Complexity

## A Cascade of Intractable Problems

10s-100s of engineers, 18-24 months of development

(c) 2024 Synopsys, Inc.

# The Reinforcement-Learning Optimization Paradigm

Al-Assisted Hardware Design Tutorial – HotChips 2024

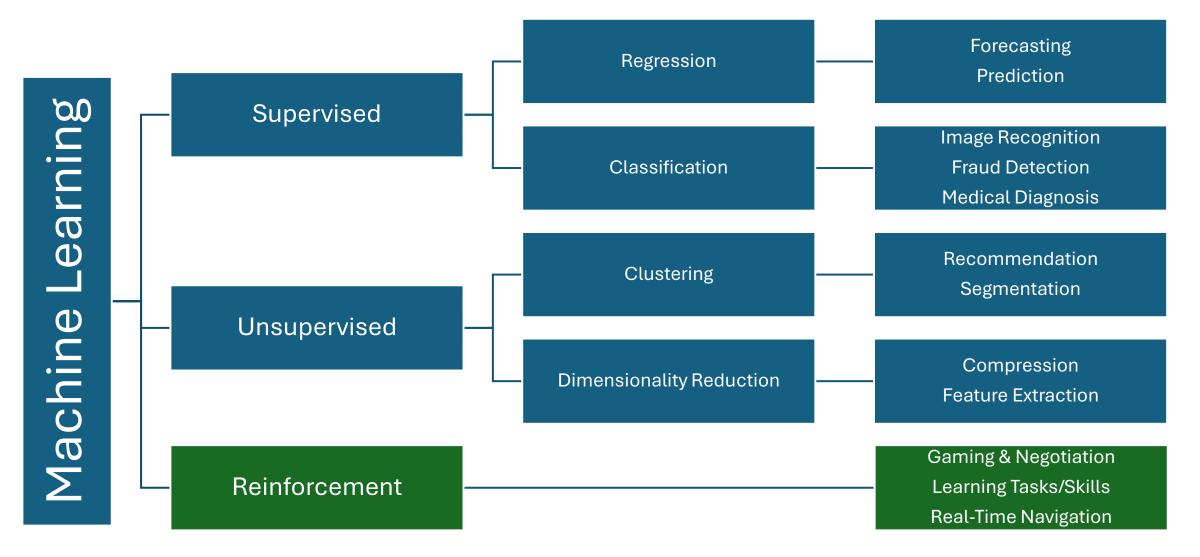

## What is Reinforcement Learning (RL)?

**SYNOPSYS**°

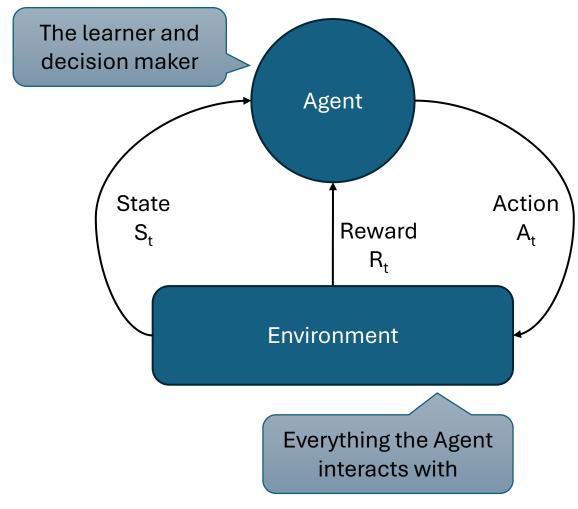

## How Does Reinforcement Learning Work?

https://www.synopsys.com/glossary/what-is-reinforcement-learning.html

**SYNOPSYS**<sup>®</sup>

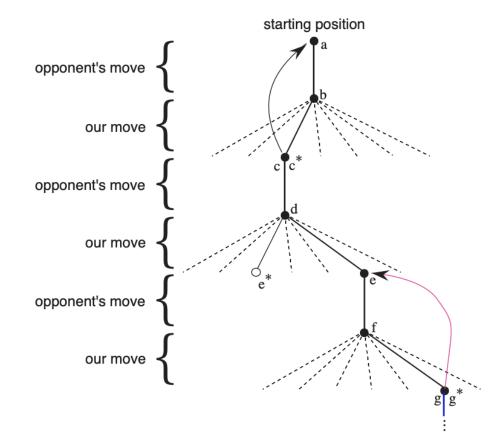

- 1) The Agent observes the environment's state  ${\rm S}_{\rm t}$

- 2) The Agent selects an action A<sub>t</sub> and applies it to the environment

- 3) The Agent receives a reward R<sub>t</sub>

- Goal is to maximize this reward over time

- 4) A new state  $S_{t+1}$  is entered

- Generally, the Agent implements a mapping from states to probabilities of possible actions

- RL algorithms can be model-based or model-free (twin)

- Value-based: Estimate value function given enough trajectories (SARSA, Q-learning)

- Policy-based: Directly estimate optimal policy (Monte-Carlo, deterministic policy gradient)

#### **Benefits of Reinforcement Learning**

Citation. Sutton, R. S., & Barto, A. G. (2018). Reinforcement learning: An introduction (2nd ed.). The MIT Press.

**SALIOHZAZ**

- Focuses on the problem as a whole

RL understands the goal, and can trade off short-term rewards for long-term benefits

- Does not need a separate data collection step

- Training data is the Agent's experience, not a separate set established a-priori

- Works in dynamic, uncertain envs

RL is inherently adaptive and built to respond to changes in the environment

RL can seek a long-term goal while exploring various possibilities autonomously

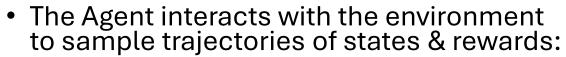

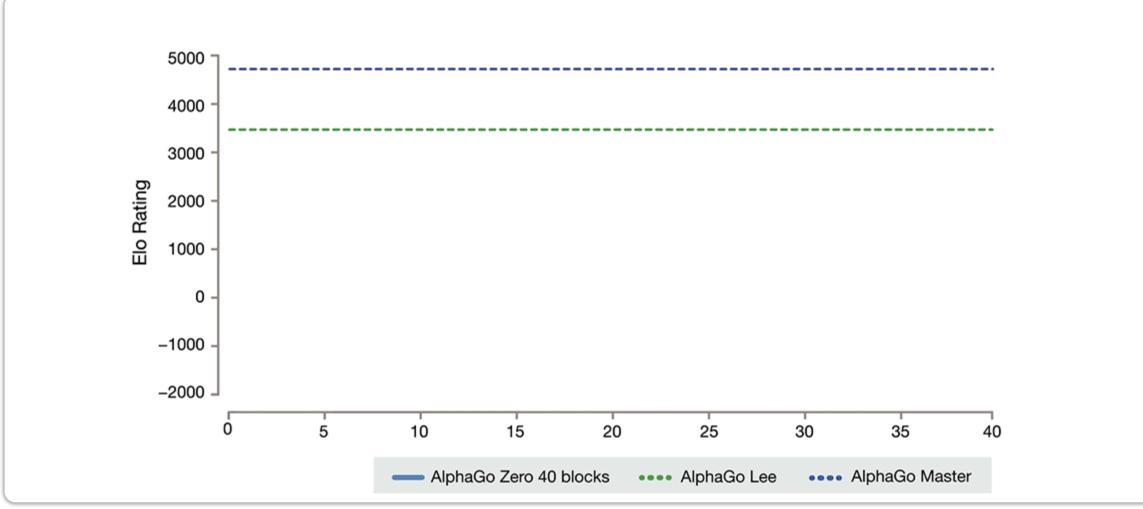

#### RL Example: Learning to Play GO

DeepMind AlphaGo goes from zero to world champion in 40 days

**SYNOPSYS**<sup>®</sup>

Example: https://deepmind.com/blog/alphago-zero-learning-scratch/

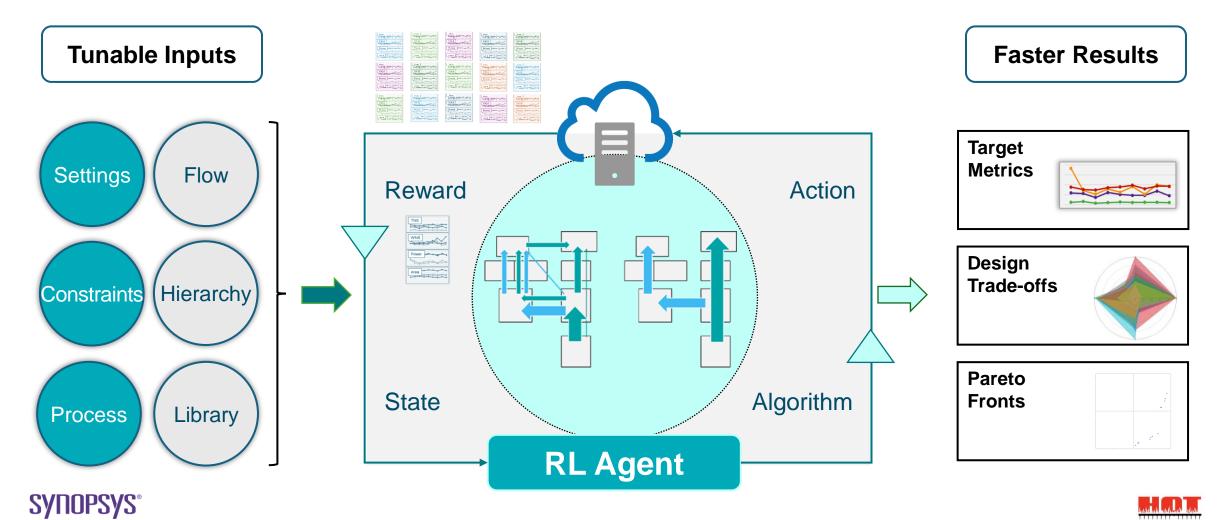

## Applying RL to Chip Design Problems

(c) 2024 Synopsys, Inc.

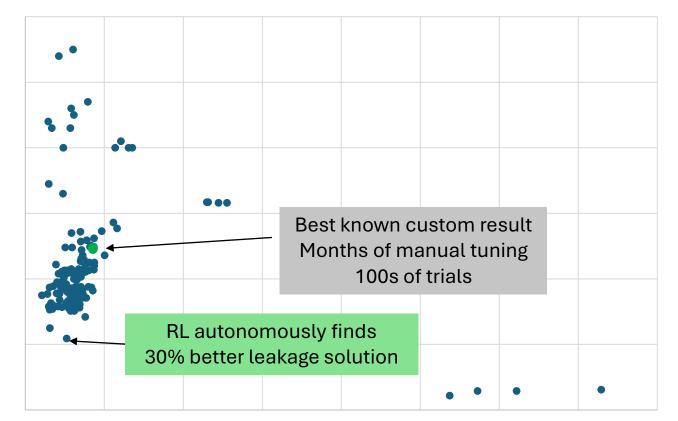

## **AI-Assisted Design Search**

TNS vs. Leakage

#### **Problem Statement:**

Achieve lower leakage while maintaining timing

#### Search Space

- Design, tool, flow parameters

- Library cell parameters

#### **Objectives (prioritized)**

- Leakage

- TNS

- Secondary (e.g. DRC etc.)

Leakage

# Applications of RL-driven Optimization

Al-Assisted Hardware Design Tutorial – HotChips 2024

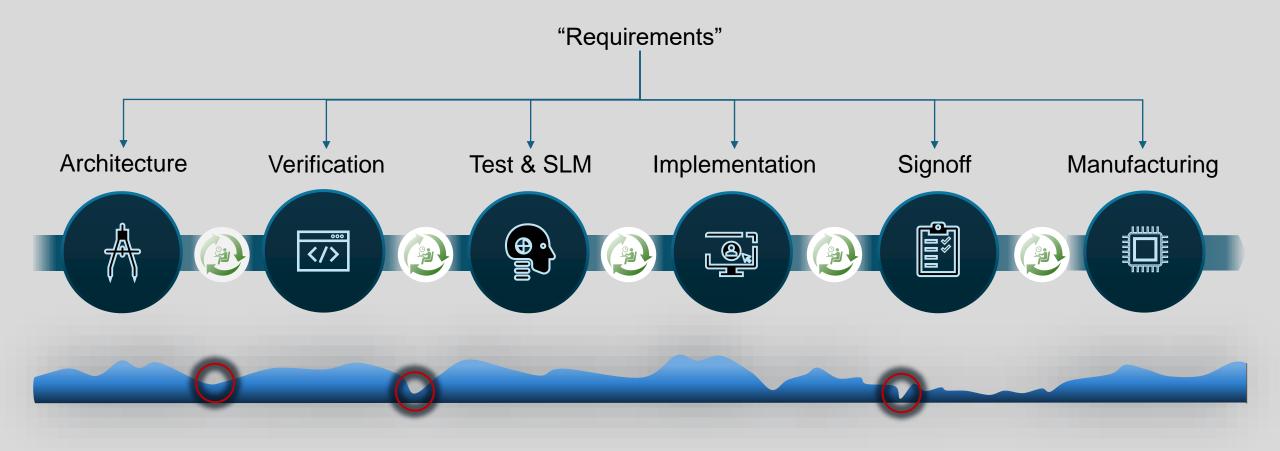

## Opportunities to Apply RL Opt. Throughout the Flow

#### **AI-Assisted Digital Implementation**

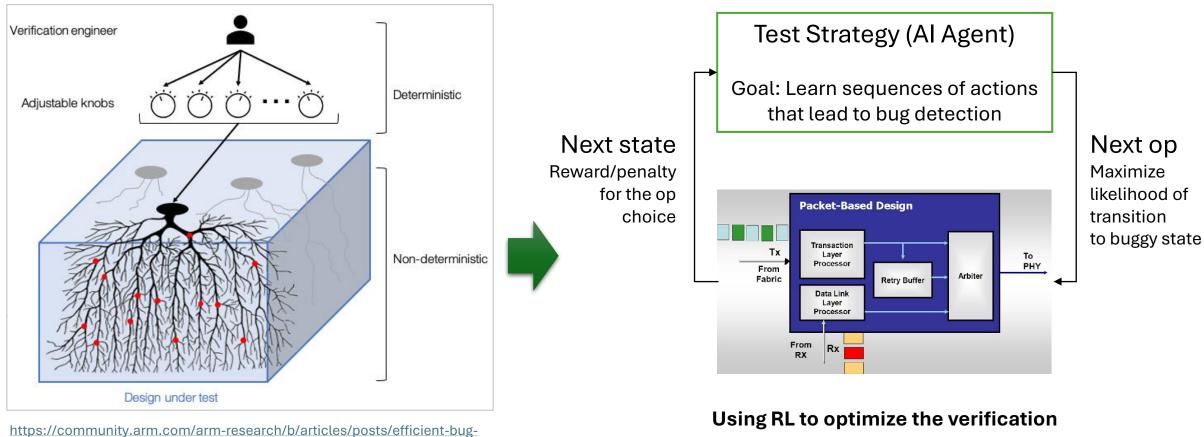

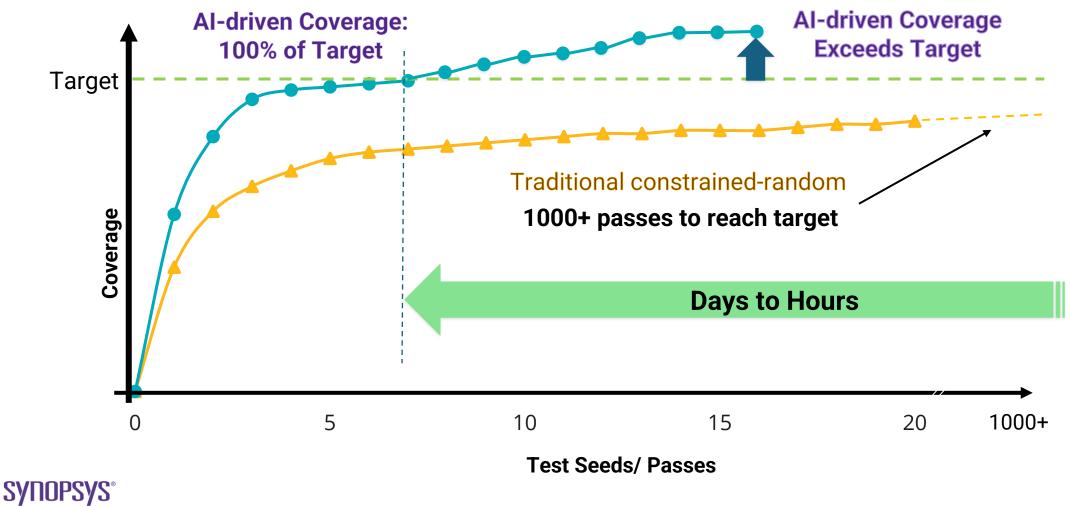

#### **AI-Assisted Verification**

process

#### **SYNOPSYS**<sup>®</sup>

discovery-with-machine-learning-for-hardware-verification

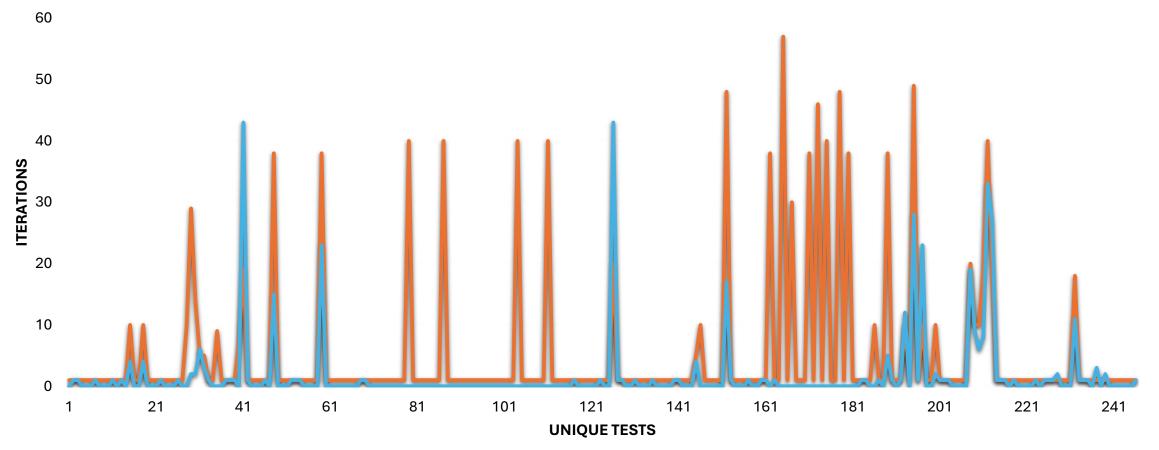

#### Example: Scheduling Highest ROI Tests

**Regression Test Distribution**

**SYNOPSYS**°

## **Enabling Faster Time To Closure**

(c) 2024 Synopsys, Inc.

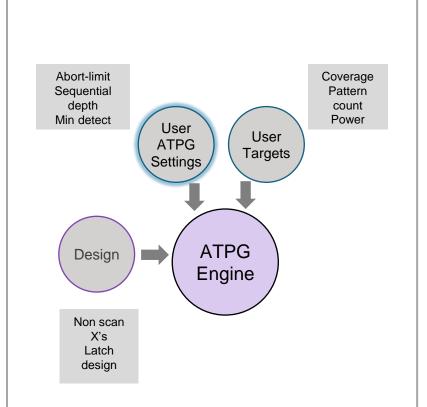

#### And Many More Applications..

#### **Circuit Optimization**

**Test/ATPG**

#### **3D Integration**

#### Autonomous multi die exploration

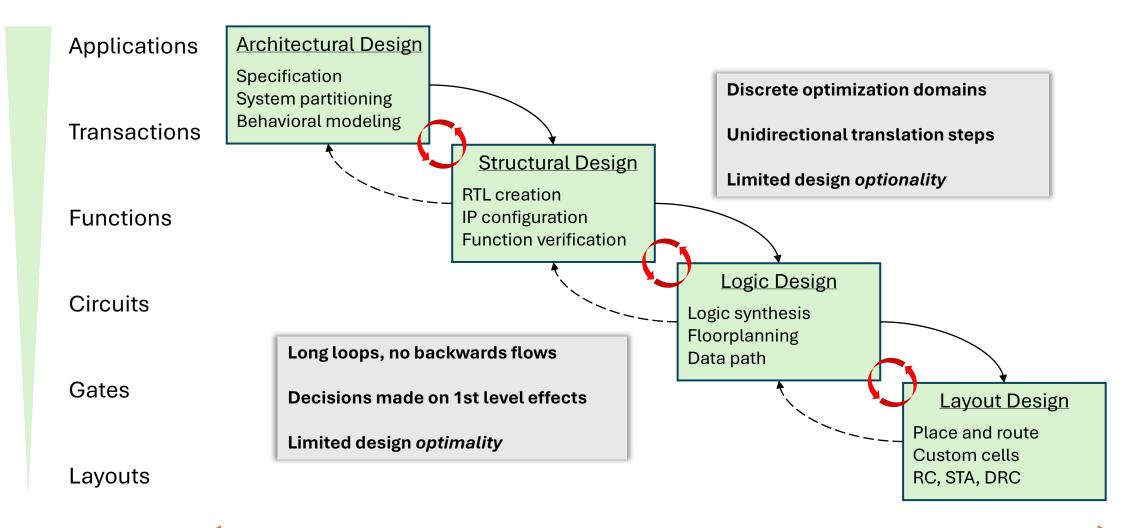

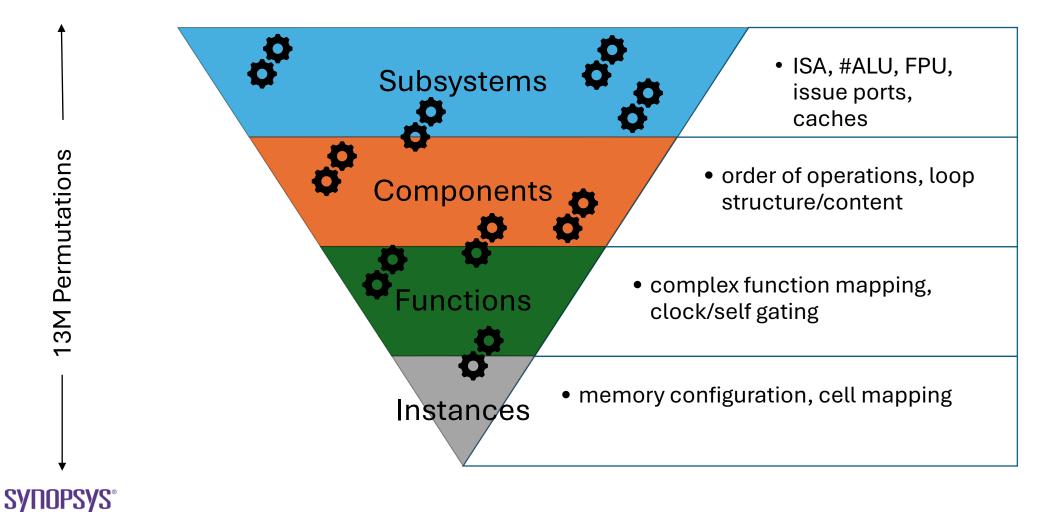

#### How About Optimizing Across Design Abstractions?

(c) 2024 Synopsys, Inc.

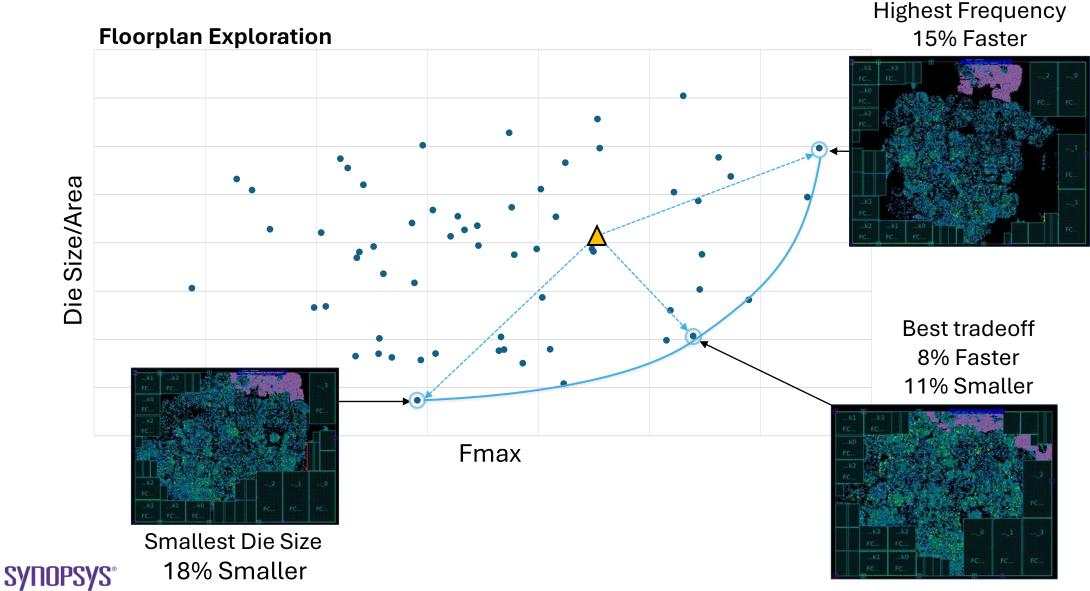

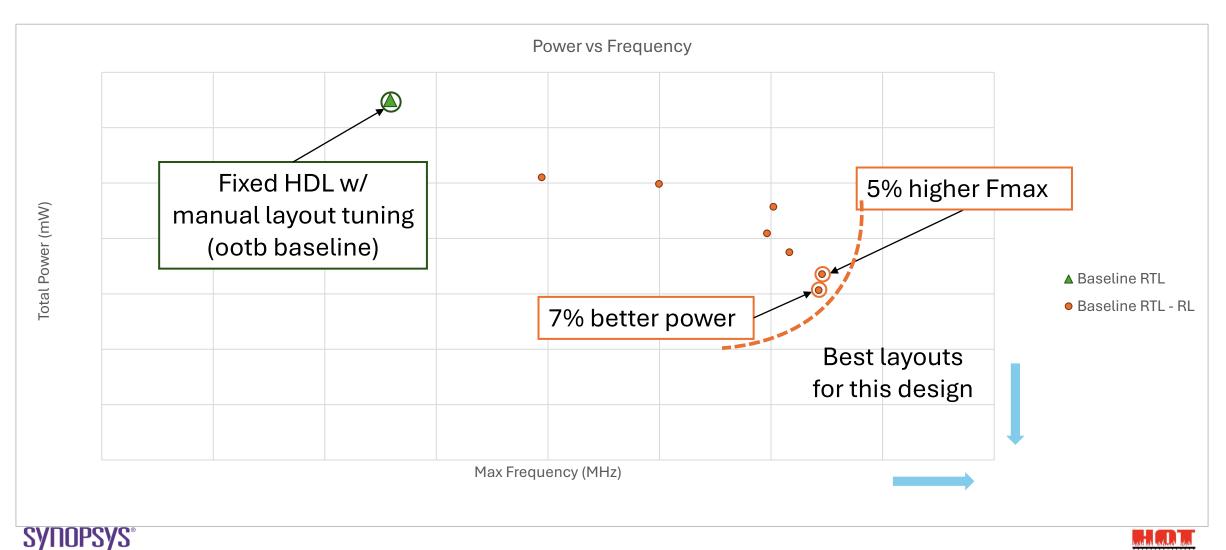

#### Single-Abstraction: RL-based Layout Opt.

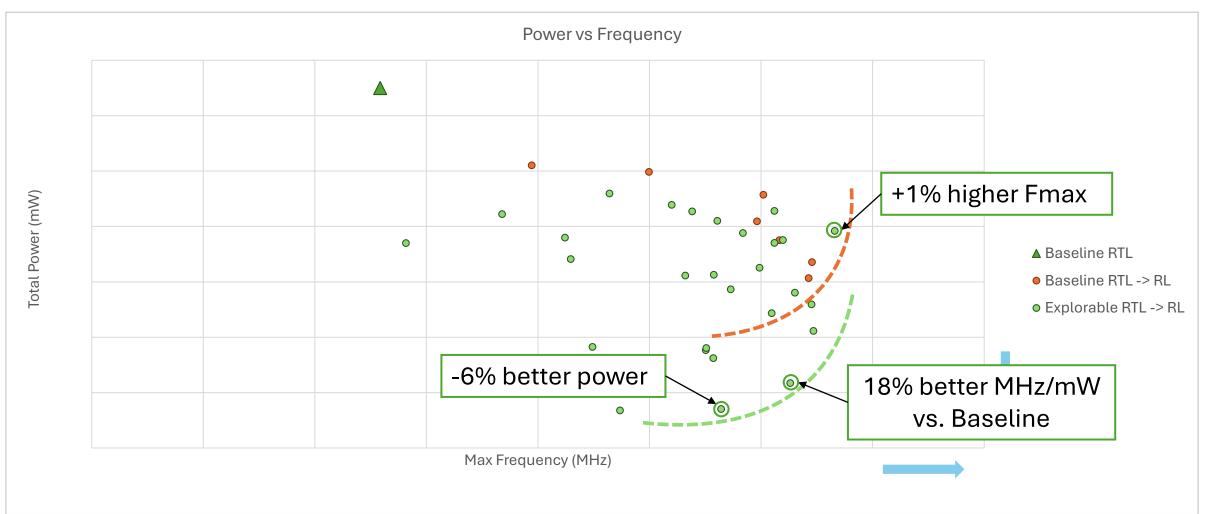

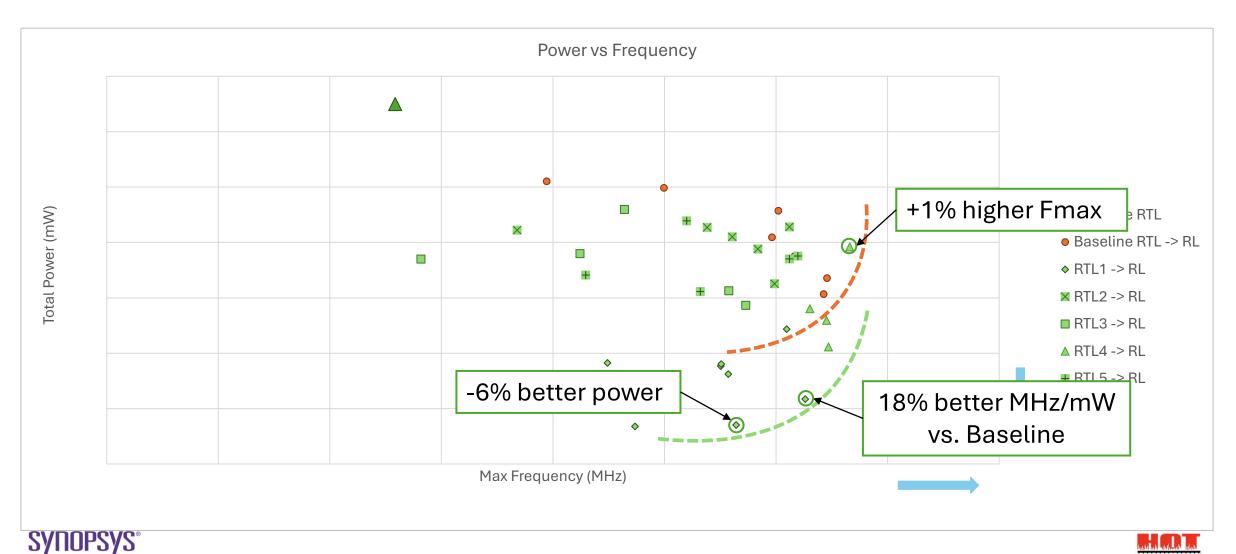

#### Multi-Abstraction: Functions-to-Layout Opt.

#### SYNOPSYS®

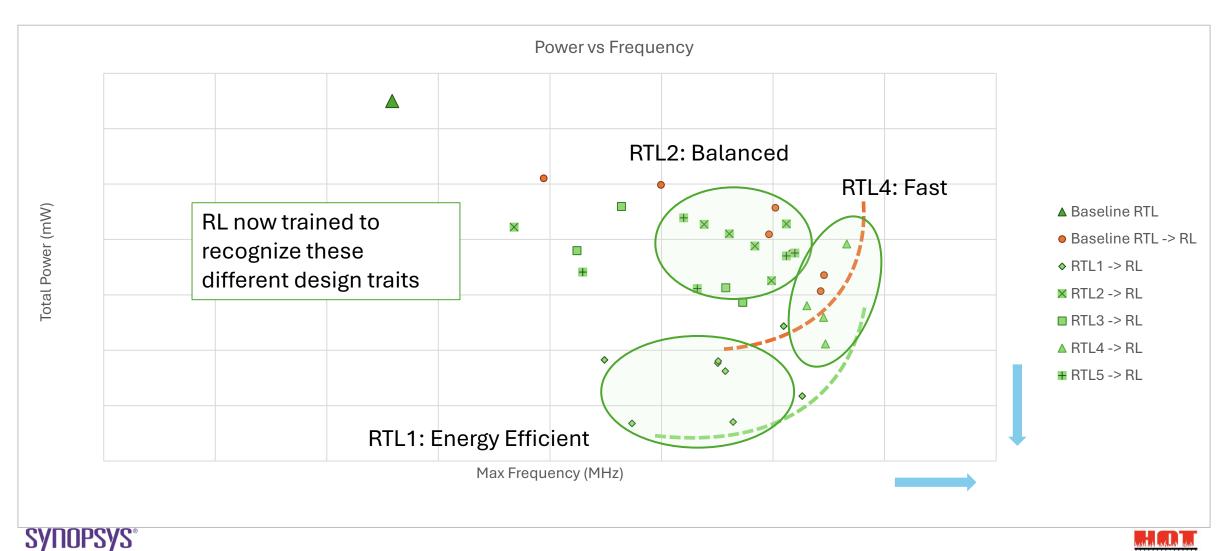

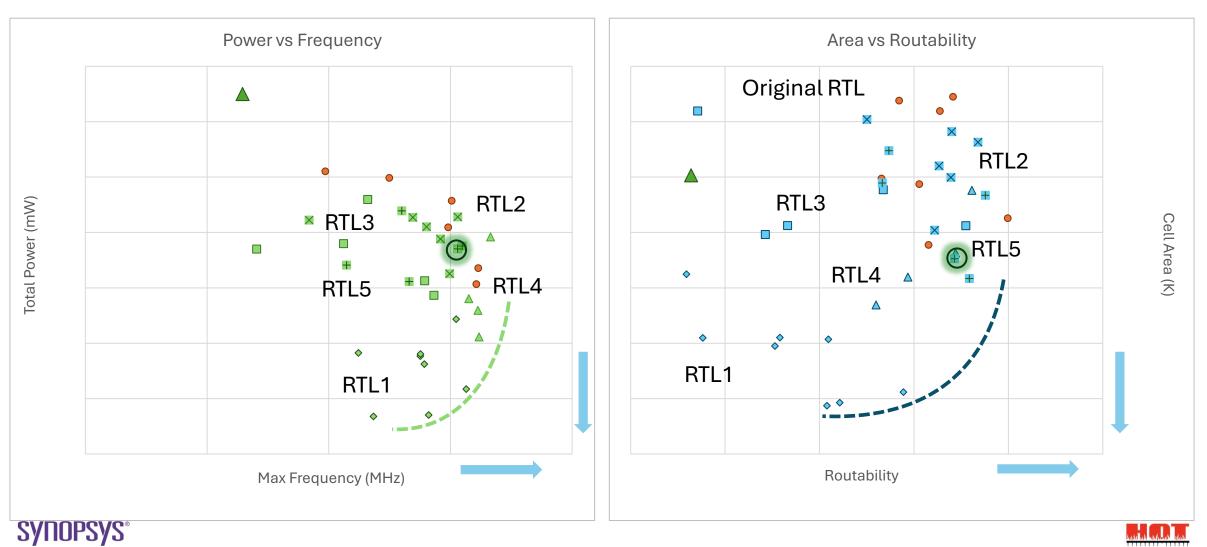

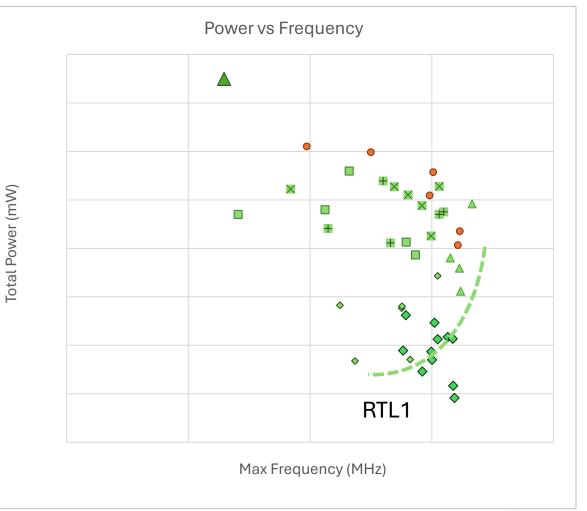

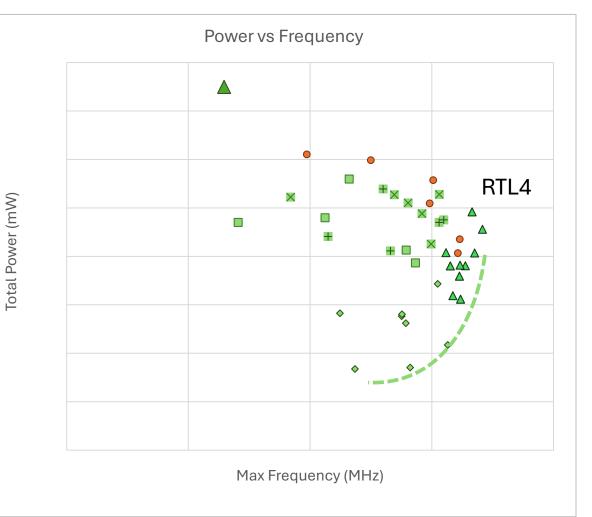

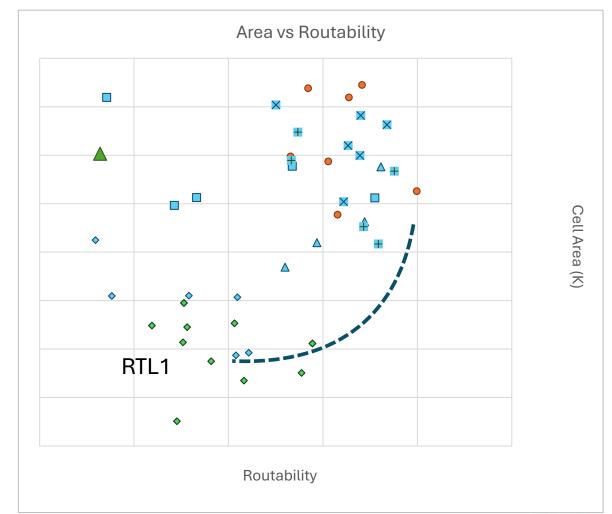

## Top-20 Results: 5 Different Design Configs

#### Functions with Different Layout Characteristics

#### So, Which Design Variant is the Best One?

(c) 2024 Synopsys, Inc.

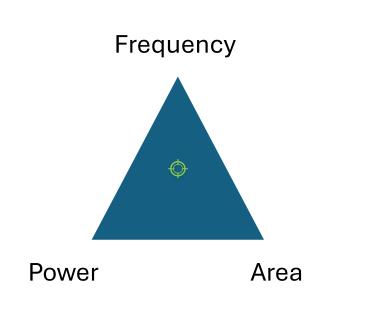

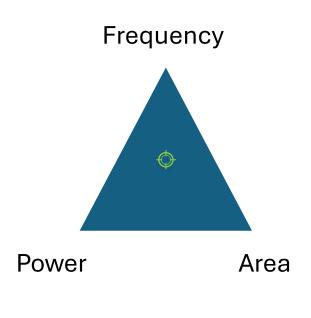

## **Recentering Design Functions-to-Layout**

Using AI to quickly traverse problem space towards 'learned' solutions

## 1) Objective: Energy Efficiency

#### **SYNOPSYS**<sup>®</sup>

## 2) Objective: Performance

## 3) Objective: Area

#### **SYNOPSYS**<sup>®</sup>

#### Limitations of the RL-based Opt. Paradigm

- 1. Creating design variants is a high-effort task

- Verifying even a single version of a design is difficult, how to scale?

- 2. Evaluating design variants can be slow

- Typically involves synthesis, P&R, timing/power/IR/etc. analysis

# Augmenting RL with GenAl – A World of Opportunity

Al-Assisted Hardware Design Tutorial – HotChips 2024

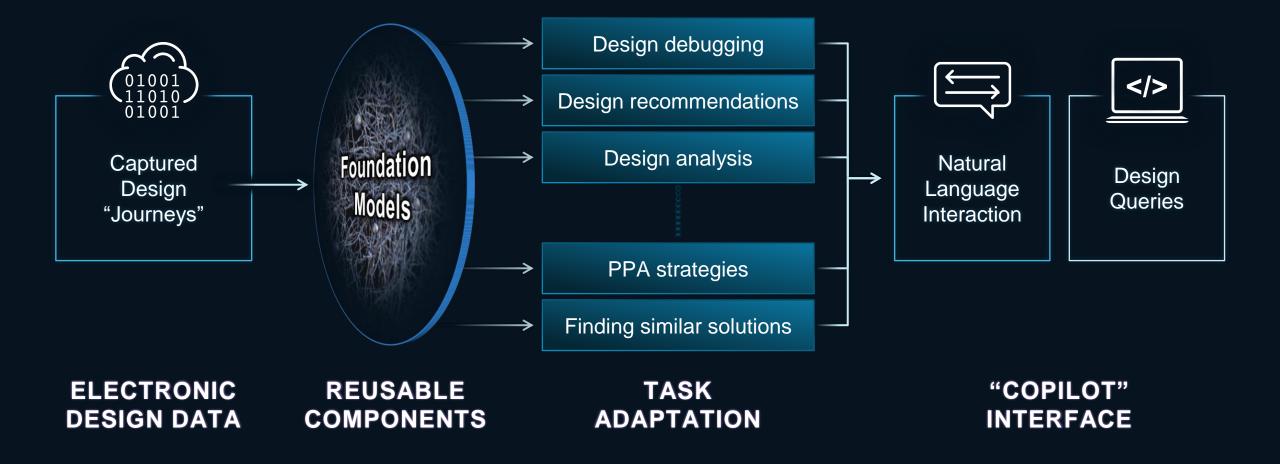

#### 2<sup>nd</sup> Wave of AI : Generative Models Coming into Play

Ref: Adapted from the Stanford Institute for Human-Centered Artificial Intelligence's (HAI) Center for Research on Foundation Models (CRFM)

(c) 2024 Synopsys, Inc.

## Augmenting RL Opt. with Generative AI

- RL (Optimization)

- Uses tool engines to create and evaluate design data on the fly

- Signoff-accurate: Results are outcomes of existing tooling

- Overall slower, relies on process-level distribution

- Semi-automatic: Requires significant effort in describing design spaces, outcome metrics

Good at identifying optimality

#### • GenAl (Generation)

- Captures data history from prior design journeys

- Speculative: Results are outcomes of trained neural networks

- Overall faster, relies on data-level parallelization

- Highly autonomous: Capable of traversing the data abstraction stack quickly, and with limited guidance

Good at generating **optionality**

#### **SYNOPSYS**<sup>®</sup>

#### Remember: Limitations of RL-based Opt.

- 1. Creating design variants is a high-effort task

- Verifying even a single version of a design is difficult, how to scale?

- 2. Evaluating design variants can be slow

- Typically involves synthesis, P&R, timing/power/IR/etc. analysis

Optionality

Optimality

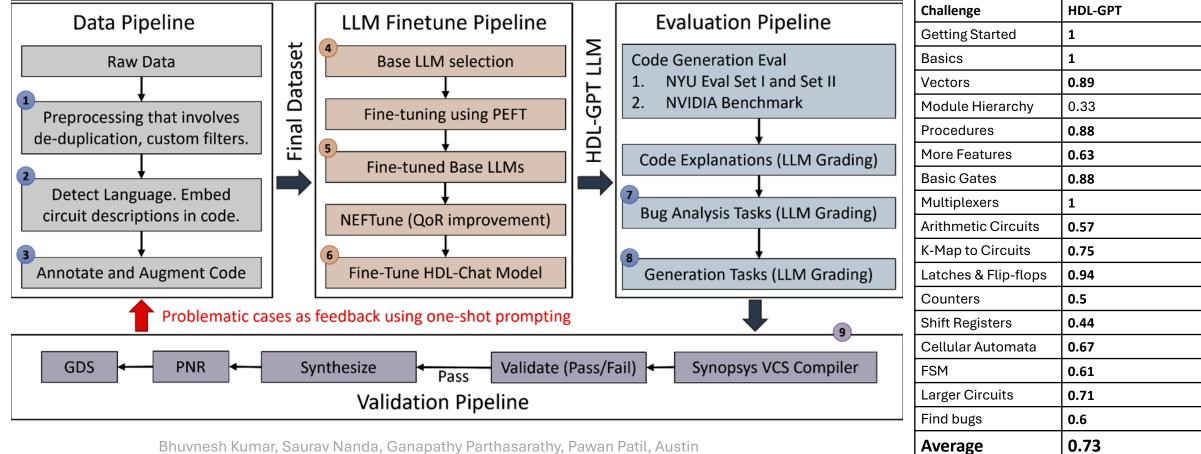

#### 1. Research in HDL Generation

Workflow for Data, Fine-tuning, Evaluation, and Verification/Feedback Pipeline for HDL-GPT

#### **Comparison vs NYU Eval Set II**

Bhuvnesh Kumar, Saurav Nanda, Ganapathy Parthasarathy, Pawan Patil, Austin Tsai and Parivesh Choudhary, "HDL-GPT: High-Quality HDL is All You Need," 2024 Design Automation Conference (DAC)

**SYNOPSYS**°

arXiv:2407.18423v1 [cs.LG] 25 Jul 2024

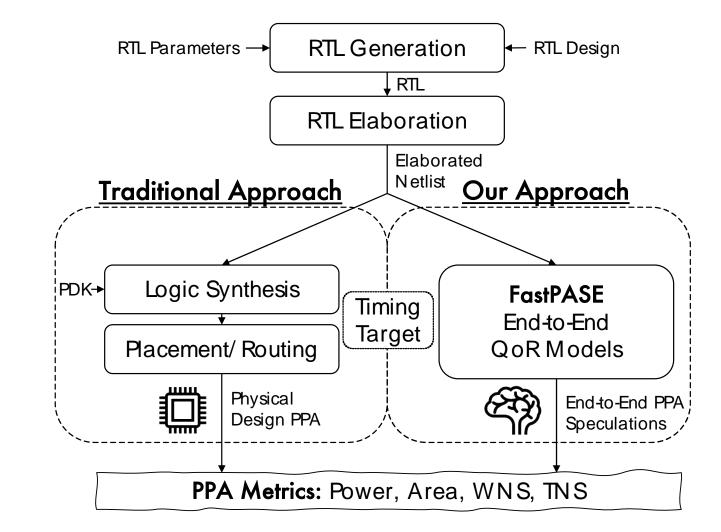

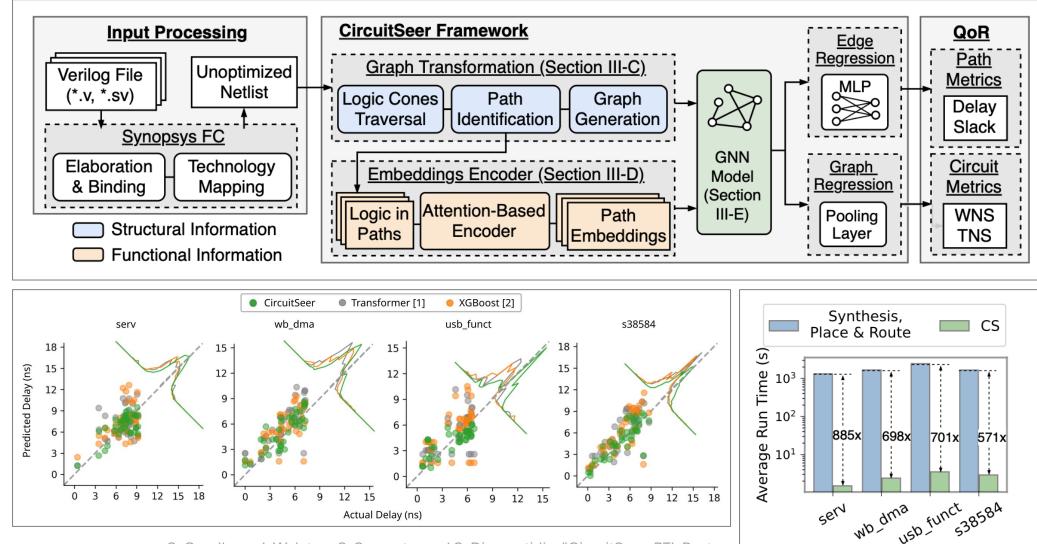

# 2. Research in PPA Speculation

- Challenge: Evaluation of design options slow, compute intensive

- Approach: Use GCNs for end-to-end PPA speculation

• 10X faster evaluation, broader and deeper search

A. Levy, J. Walston, S. Samanta, P. Raina and S. Diamantidis, "FastPASE: An AI-Driven Fast PPA Speculation Engine for RTL Design Space Optimization," 2024 25th International Symposium on Quality Electronic Design (ISQED)

#### Using GCNs to Accelerate Design Evaluation

**SYNOPSYS**°

S. Gandham, J. Walston, S. Samanta, and S. Diamantidis, "CircuitSeer: RTL Post-PnR Delay Prediction via Coupling Functional and Structural Representation" 2024 ICCAD (accepted) (c) 2024 Synopsys, Inc. >500X faster exploration TAT

Optimality

## Summary – AI-Assisted Design

- RL has enabled the 1<sup>st</sup> wave of AI in chip design (optimization)

- Applications up and down the data abstraction stack

- GenAl is opening up opportunities to tackle the design process holistically

- Traverse data abstractions more efficiency

- Next level challenges emerge

- High-level planning driven by reuse, past experiences

- Fast assessment of design quality for functional correctness and performance

- Technology advancing very rapidly, accelerating pace of AI-assisted design

#### **SYNOPSYS**°

## Thank you!

(c) 2024 Synopsys, Inc.